# Actions MICROELECTRONICS Co., Ltd.

Actions-micro AM8268N Datasheet

Document Number: AM8268N Datasheet Revision 1.0.0 Release date: 12/01/2018

Actions Microelectronics Co., Ltd. 506, 5floor, Golder Plaza, No.10 huayuandonglu, Haidian District, Beijing, China

Revision History

| Version | Date       | Description    | Author    |

|---------|------------|----------------|-----------|

| 1.0     | 06/27/2018 | Initial Create | maweishuo |

# **1** Introduction

### 1.1 Overview

The AM8268N processor from Actions-Micro is a highly integrated mix signal SoC target at multi-media applications. The AM8268N emmedded CPU is a high performance, low power 32bit RISC core with DSP instruction extension, which can run as fast as 800MHz.

The AM8268N processor features a hardwired multi-format video decoder, which supports a large variety of popular video formats including: H.264, RMVB, MPEG1/2/4 and VC1 at full HD resolution. The AM8268N integrated image/video post processor and display engine provide a powerful image processing ability, such as seamless zoom in/zoom out, cropping, rotation, color space conversion, gamma correction, edge enhancement, dithering, brightness, contrast and saturation adjustment. Moreover, a configurable FIR is reserved for other special effects extension. The 2 layers of OSD window can be configured as large as full screen and the color depth is ranging from 1 bit to 32bit true color.

The AM8268N multi-media processor provided display solutions: with the help of on chip HDMI.

AM8268N is also integrated with a DDR2/DDR3 SDRAM controller, 1 USB OTG controllers, UART, I2C, SPI,etc.

There is a 512Mb DDR2 memory die integrated in AM8268N, so no need to hang a DDR2 memory on PCB.

# 2 Feature

The AM8268N provides high level of system integration to support a wide variety of applications. The features of the AM8268N include:

#### ✓ 32BIT RISC CORE

- 32K byte instruction cache and data cache

- F/W can program from DC up to 800MHz transparently

- DSP instruction for multi-media acceleration

- Static design allows changing clock at run-time for power saving

#### ✓ VIDEO DECODER

Multi-format supported including:

| H.264 profile and level         | Up to High Profile , levels 1-4.1                                                     |  |

|---------------------------------|---------------------------------------------------------------------------------------|--|

| MPEG-4 visual profile and level | Advanced Simple profile(frame picture), levels 0-5                                    |  |

| H.263 profile and level         | Profile 0, levels 10-70. Image size up to 720x576, time code extensions not supported |  |

| VC-1 profile and level          | Simple and Main profile; low, medium and high levels                                  |  |

| MPEG-2/MPEG-1                   | Main profile; low and main levels, MPEG-1<br>D-picture not support                    |  |

| RV8/9/10                        |                                                                                       |  |

- 30 frames per second at 1920x1080 resolution for all format

- Adaptive De-interlacing

#### ✓ JPEG DECODER

- Support JPEG baseline

- Support YCbCr 4:2:0 planar and semiplanar

- Support YCbYCr & CbYCrY 4:2:2 interleaved

- Support image size: from 80x16 to 4672x3504

- Support rotate: +90°, -90°

#### ✓ IMAGE/VIDEO POST PROCESSOR

- Image up/down scaling at arbitrary non-integer scaling ratio

- Separate scaling ratio for horizontal and vertical dimensions

- Image cropping

- Image crossing

- Image rotation, 90 180 and 270 degrees and horizontal/vertical flip

- Image mask, output image writing can be prevented on two rectangular areas

- Support YUV444/YUV422/RGB888/RGB565 for mask window for alpha blending(256 level)

- YUV/RGB conversion

- Maximum output image size up to 1920x1080

#### ✓ Display Engine

- YCbCr/RGB conversion, user definable conversion coefficients

- Image up scaling at arbitrary non-integer scaling ratio

- Separate scaling ratio for horizontal and vertical dimensions

- brightness, contrast and saturation adjust

- Edge enhancement

- Dynamic contrast adjust

- Direct mapped Gamma correction for RGB channel separately

- 24bit to 16/18 bit Bayer pattern/1D/2D method dithering

- Support progressive and interlace input format

- Support YUV4:2:2(interleave), YUV4:2:0(semi planar), RGB565, RGB888 input forma

- 16x16 hardware cursor

#### ✓ OSD

- Two layers of OSD window with overlap

- 8 level alpha blending for each window

- 1,2,4 or 8 bits OSD bitmap data width

- Transparency pixels allowed in OSD window

- Two configurable OSD palettes

- Each one of the 2 OSD windows can fetch RGB565/ARGB8888 data from system memory directly

#### ✓ DISPLAY INTERFACE

- HDMI Tx support, industry standard compliance HDMI 1.2

- Support output size up to 1920x1080

- Configurable horizontal sync interrupt

#### ✓ AUDIO

- Multi-format audio decoder:MP1/MP2/MP3/WMA/AAC/AMR-NB/WAV/PCM/ADPCM

- Build in Stereo 18-bit Sigma-Delta DAC: SNR>92db(no a-weight), 18bits,sample rate 8/12/11.05/16/22/24/32/44.1/48

- Support 32 levels volume control

#### ✓ MEMORY CONTROLLER

- Integrated with a 512Mb DDR2 die which is up to 1066Mbps

- OTP ROM 64bit Chip ID

#### ✓ DMA CONTROLLER

- 8 physical channels and 4 bus channels

- Stride mode support

- Software configurable priority

#### ✓ Boot ROM

- On chip boot ROM with boot loader

- The system could be loaded from SPI Nor flash

#### ✓ USB 2.0 OTG

- Complies with Universal Serial Bus Specification. Revision 2.0.

- Complies with On-The-Go Supplement to the USB2.0 Specification Revision 1.0a.

- Supports point-to-point communication with one low-speed, full-speed or high-speed device in Host mode.

- Supports full-speed or high-speed in peripheral mode.

- Supports USB Mass Storage Class Bulk-Only Transport Revision 1.0 as host or device.

- Supports Electronic still picture imaging Picture Transfer Protocol (PTP)

- Supports direct print function using pict-bridge

- Supports Universal Serial Bus Device Class Definition for Printing Devices Version 1.1 as host

- Supports Universal Serial Bus Still Image Capture Device Definition Revision 1.0 as host

- Configurable/programmable size of endpoints.

- Configurable/programmable single, double, triple or quad buffering.

- Programmable type of endpoints.

- Supports high-speed high-bandwidth Isochronous and Interrupt transfer.

- Supports suspend, resume and power managements function.

- Support USB wakeup

#### ✓ OTHER INTERFACE

- UART/I2C/SPI

- 3 external interrupts

- 41 configurable GPIO shared with function pins

#### ✓ POWER

- 1.3v for core

- 3.3v/1.8v for IO

- Build in 1.5v bandgap reference

- Core PLL, LCD PLL, Audio PLL and DDR PLL support spread spectrum

#### ✓ PACKAGE

- QFN 68(epad)

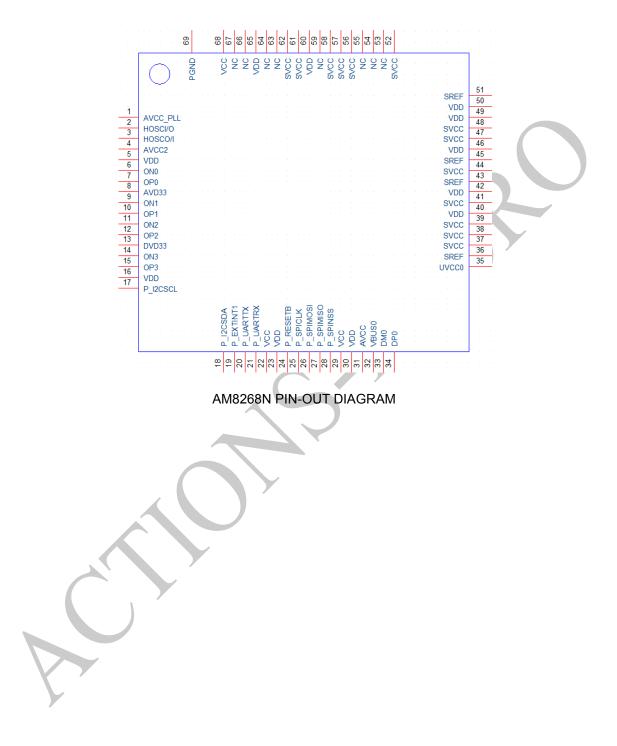

## 5.2 Pin out diagram